92. 다음 중 RIP(Routing Information Protocol)에 대한설명으로 옳지 않은 것은?

① 정적(Static) 라우팅 프로토콜이다.

② 일반적으로 도착 가능한 최대 홉 카운트는 15이다.

③ 거리 벡터(Distance Vector) 알고리즘을 기반으로 한다.

④ RIP를 사용하는 라우터에서는 일반적으로 일정주기로 라우팅 테이블을 업데이트한다.

■ 해설

- Routing Information Protocol 의 약자로, 거리벡터 알고리즘을 기반으로 개발된 동적 라우팅 알고리즘이다. 인접한 라우터의 라우팅 테이블 정보를 수집해 저장하고, 수집한 정보에서 Hop Count 가 가장 작은 경로로 라우팅 IGP(Internal Gateway Protocol) 로 많이 이용되는 프로토콜이기도 함

- RIP 특징

- Hop Count 를 기준으로 Hop Count 가 가장 최적의 경로를 찾는다(최대 Hop Count 15)

- 자신의 라우팅 테이블을 30초 주기로 전파한다

- Hop Count 는 0부터 15까지, 16은 무한대 라는 뜻을 가진다

- RIP 는 라우팅 경로의 속도와는 무관하다(Hop Count 고려)

* Hop Count : 라우터를거친 수, 라우터를 하나 거칠 때마다 1씩 증가하는 수치

|

구분

|

정적 라우팅

|

동적 라우팅

|

|

관리

|

|

|

|

인터페이스

|

|

|

|

중간경로

|

|

|

|

구분

|

Distance Vector(거리백터)

|

Link State(링크상태)

|

|

패킷전송

|

|

|

|

경로

알고리즘 |

|

|

|

경로 설정

|

|

|

|

주요 매트릭

|

|

|

|

업데이트

시점 |

|

|

|

적용

|

|

|

|

장점

|

|

|

|

단점

|

|

|

|

대표

프로토콜 |

|

|

정답 : ①

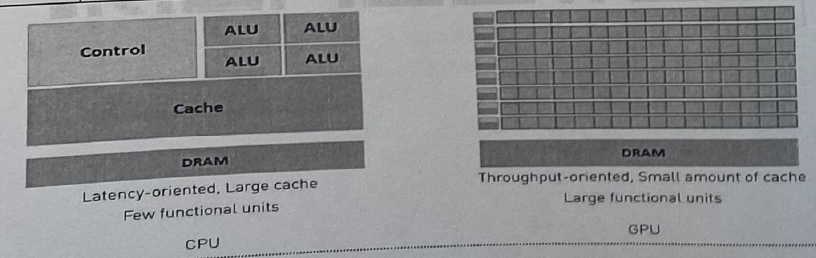

93. 다음 중 GPU 컴퓨팅에 대한 설명으로 가장 적합하지 않은 것은?

① GPU는 자체 지역메모리를 사용한다.

② GPU는 고도의 하드웨어 멀티스레딩(multi-threading) 을 사용한다.

③ GPU를 사용하기 위해 CUDA와 같은 플랫폼을 사용할 수 있다.

④ GPU는 메모리 지연시간을 극복하기 위해 중앙처리장치를 사용한다.

■ 해설

- GPU 는 메모리 지연시간을 극복하기 위해 중앙처리장치를 사용하지 않고 아래와 같은 방법 활용

- 고도의 하드웨어 멀티스레딩 활용

- 병렬 연산 활용(CUDA 는 NVIDIA 의 병렬 컴퓨팅 플랫폼

- 전용 메모리 계층을 활용하여 접근 시간 단축

|

구분

|

CPU

|

GPU

|

|

설계 목적

|

|

|

|

캐시의 역할

|

|

|

|

Latency

관리 |

|

|

|

멀티쓰레딩

|

|

|

|

메인 메모리

대역폭 |

|

|

정답 : ④

공감과 댓글은 아이티신비에게 큰 힘이 됩니다.

블로그 글이 유용하다면 블로그를 구독해주세요.♥

'정보시스템 감리 기출해설 > 시스템 구조 해설' 카테고리의 다른 글

| (제 25회) 시스템 구조 / (96)~(97) 해설 (0) | 2025.02.16 |

|---|---|

| (제 25회) 시스템 구조 / (94)~(95) 해설 (0) | 2025.02.15 |

| (제 25회) 시스템 구조 / (90)~(91) 해설 (0) | 2025.02.13 |

| (제 25회) 시스템 구조 / (88)~(89) 해설 (1) | 2025.02.12 |

| (제 25회) 시스템 구조 / (86)~(87) 해설 (0) | 2025.02.11 |